发布时间:2011-05-25

发布时间:2011-05-25

网关设备CPU架构发展历程

网关设备CPU是伴随着网关设备的发展而演进的。在网关设备的不同发展阶段,由于设备具备的功能复杂度不同、性能要求不同,对CPU的要求也随之不同。

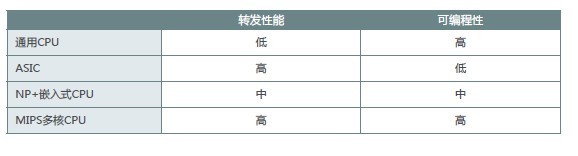

1) 通用CPU架构。在网络发展早期,承载业务种类较为单一,例如简单的文件传输、邮件、信息发布等,而且带宽普遍不高。此时对网关设备要求非常简单,只要能进行IP转发即可,如果能同时附带支持一些附加功能更好,如NAT、QoS。由于对网关设备要求不高,不关注吞吐,相应的CPU要求也不高,很多网关设备采用通用架构CPU甚至直接由PC改装。

2) ASIC架构。随着网络的发展,承载的业务种类开始增多,带宽开始增大,网络的管理和运营走向前台。此时对网关设备的吞吐量、管理提出较多要求。由于开始关注网关设备的转发性能,通用CPU已经无法满足了,此时专业的网关设备开始采用A S IC架构以满足网关设备对高性能的要求。但其缺点也十分明显。由于网关设备需要处理各种各样的应用,ASIC开发周期长、研发费用高成为其致命伤。所以,这种架构比较适合模式简单,对性能和吞吐量要求较高的网络,但无法满足网关设备的需求。

3) NP+嵌入式CPU架构。最初,各厂商曾尝试采用NP代替ASIC,原因在于NP在保留ASIC的高吞吐的特性同时具备简单的可编程能力。这样,设备可以在保证吞吐不受影响的情况下进行一定的智能处理。但是NP的可编程能力有太大局限性,导致设备智能处理能力较弱,依然无法满足用户对网络的期望。

4) MIPS多核CPU架构。基于以上背景,MIPS多核架构开始被部分厂商实践,由于MIPS多核架构的CPU在内部是由多个嵌入式CPU组成的,同时兼顾高可编程性和高报文处理性能。从而使得设备在保证高吞吐的前提下可以进行更复杂的智能处理动作,进一步的贴近了用户的需求。

锐捷网络MIPS多核架构实现

锐捷网络出口网关全线产品NPE、ACE、EG、NBR均采用MIPS多核CPU架构,既可以保证高性能,又能够保证多业务。

多核并发处理

在单核平台下,报文转发和设备本机业务一直处于一种博弈状态,各设备厂商只能通过软件系统来寻找平衡和规避。

采用了多核处理器,以上问题便可迎刃而解。CPU所有核并发工作,同时独立处理不同的业务,互不干扰,最大限度的发挥CPU的处理能力,实现转发性能的倍增。

锐捷网络多核并发处理的两个关键技术是:独立管理核与虚线程。

1) 独立管理核的本质是拿出一个独立的核专门执行管理层面的处理,这样可以保证无论当前转发业务处理多么繁忙,用户均能自如的访问设备并进行管理。从物理资源上对用户管理设备进行了保证。

2) 虚线程是将几个核的线程融合到一起,但这种融合并不是简单的叠加,而是将芯片进行优化,缓存共享,并且有专用的硬件进行加速,从而大大提高转发效率。由于线程是最有效的规避内存和I/O访问延迟的方案。通过多转发线程并发,最大限度的规避内存和I/O访问延时,最大限度的实现真正的内核级的并发,充分利用CPU资源。

硬件加速

通过软件架构的优化来系统处理性能,难度大,且提升幅度有限。目前业界常见的提升网络系统性能还是依赖硬件性能的提升。多核处理器一般都会内置一些实用的硬件加速引擎辅助处理器内核进行工作。锐捷网络所使用的MIPS多核处理器包含如下硬件加速引擎,这些引擎运行时并不消耗CPU资源。

1) 智能报文分发引擎:多核架构并发的基础是要保证所有核都运行,不至于出现某些核一直空闲,而另一些核一直处于超负荷状态。锐捷网络使用的多核CPU内置的智能报文分发引擎,能根据设置的规则,将报文送不同核处理,同时保证每个核的负载均衡。常见的分发策略如下:

√ 将接收的报文立即发送到当前空闲的核处理。

√ 依据特定的需求,将报文发送到特定核处理。

2) 硬件加密:随着网络业务普及,越来越多的业务对安全性提出了要求,这样对I Ps e c等加密转发协议的需求越来越紧迫。而传统的采用CPU进行IPsec的加解密处理的性能是完全不可接受的。多核CPU内置的加密引擎有效地解决了这个问题,使加解密过程对转发的影响降低。加密引擎支持AES、DES/3DES、SHA-1、SHA-256、MD5 等业务主流加密算法。

3) 硬件压缩/解压缩:压缩/解压缩主要用于两个大的业务——内容审计与应用交付。对于开启内容审计的用户,压缩的信息需要解压缩后才能审计,而软件解压缩非常消耗性能,通过硬件加速后,可以大幅提供内容审计的效率。目前常见的应用交付功能主要是采取压缩报文发送,接收端解压缩后再转发内网。通过硬件加速后,压缩和解压缩对转发的影响降低。

4) 硬件TCP/UDP加速:对于某些需要修改报文四层载荷的业务,如N AT等,修改后需要重新计算四层头的校验和,这也是一个比较消耗时间的工作。通过硬件加速后,提升了诸如NAT转发的性能。

小结

由于多个CPU,且均可独立编程,具备了高度的灵活性。并且因为每个CPU可以独立运行不同业务,从而实现了复杂业务的并发处理。而且目前常见的多核CPU一般都具备特定业务的硬件加速,如加密等,这样就可以更好提升特定业务的处理性能。

相比较而言,MIPS多核架构的出现,是一种思路上的转变,在CPU的功能和性能之间找到了一个平衡点,同时还兼顾到了硬件加速的思路。

出口网关设备处于网络拓扑中极其特殊的位置,由于其既要求具有如流控、智能选路等复杂的功能,又要求极高的转发性能。所以,MIPS多核架构必然成为网关设备未来发展的主流趋势。